|

| Home │ Audio

Home Page |

Copyright © 2011, Free use of program governed by statement in

About dialog which is repeated below.

Updated June 2, 2012. See Document History

at end for details.

SPICE verified.

FETCurve

Introduction

In the context of desiring to match or scale FET parameters for the

purpose of distortion cancelation, it becomes desirable to calculate

these parameters. Few would have access to transistor testers for

their high cost. Here I show how these parameters can be

calculated from measurements made with just a power supply and a

multimeter and provide a dedicated calculator to make them.

Calculations

These calculations are exact for

enhancement MOSFETs. The program makes minor adjustments for

JFET's depletion mode bias range.

Simple Calculations are

based on the idea that the VGS measured with the highest

bias resistor is approximately VT. RBIAS

determining VT would have to be very high compared to any

anticipated circuit bias like 1MΩ. The other measurement would

then determine kn (or KP in SPICE terms).

If VGS1 ≈ VT then

| (1) |

ID2 = |

VBIAS - VGS2

RBIAS2 |

| (2) |

kn = | ID2

(VGS2 - VT)2 |

Two-Point Calculations mathematically fit a curve to the data

instead. Three data points are usually required to define a

second order polynomial. Two data points suffice because a

constant preexisting boundary condition satisfies the function of the

third data point. That di/dv = 0 when i = 0 at VT

defines this boundary condition.

If the MOSFET equation

| (3) |

ID = kn(VGS - VT)2 |

is rearranged in the form

| (4) |

|

+ VT = VGS |

A pair of simultaneous non-linear equations suitable for solving for kn and VT can be written:

| (5) |

|

+ VT = VGS1 | ||

| (6) |

|

+ VT = VGS2 |

The following substitutions in the rearranged MOSFET equation

| (7) | x0 = |

|

||

| (8) | x1 = | VT | ||

| (9) | aX0 = |

|

||

| (10) | aX1 = | 1 |

||

| (11) | aX2 = | VGSX |

where X is the data point and equation number, yields solvable

simultaneous linear equations in the form of:

| (12) |

a10x0 + a11x1 = a12 |

| (13) |

a20x0 + a21x1 = a22 |

or in standard matrix form:

| (14) |

|

|

|

Continuing with the substitutions in the matrix:

| (15) |

|

|

|

By matrix reduction, the matrix is transformed to diagonal format

with the last column containing the results:

| (16) |

|

|

|

Because the reduced a22 term returns VT in its

final form, it remains only to solve for kn from the reduced

a12 term.

| (17) |

kn = |

1

a122 |

Calculator

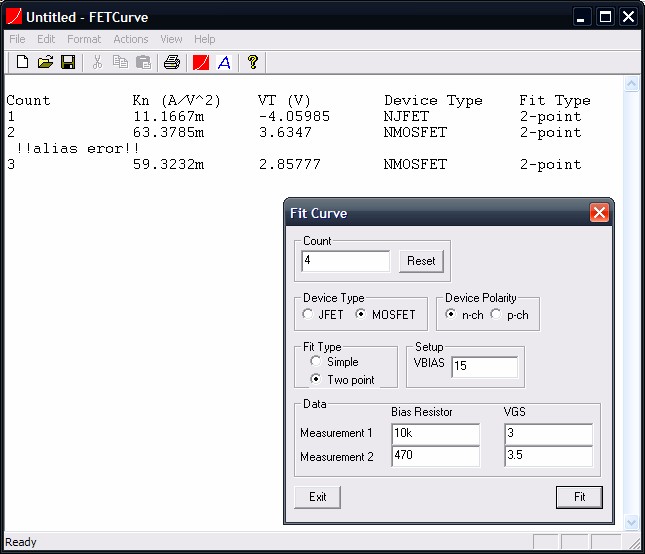

Based on above calculations, I am offering a simple calculator for

download. It is tested in Windows XP, Windows 98, and under Linux

using Wine (Windows Emulator)1

as well.

|

|

EULA

I retain copyright. You may freely use this software for

personal, non-commercial, use (that is you cannot offer it for

sale). You may share it with others as long as it is provided to

them complete and unmodified as you get it from this website.

Because this program is free, although it works, I do not guarantee its

operation or application

Download

| Download FETCurve 1.2.1.zip (13KB) | |

| Download FETCurve 1.1.0.zip (12KB) | |

| Download FETCurve 1.0.0.zip (12KB) |

After download, copy the executable into the desired

directory. You will have to manually create links on the desktop

or the start menu, as you desire.

Instructions

(These are to serve in place of a program help file)

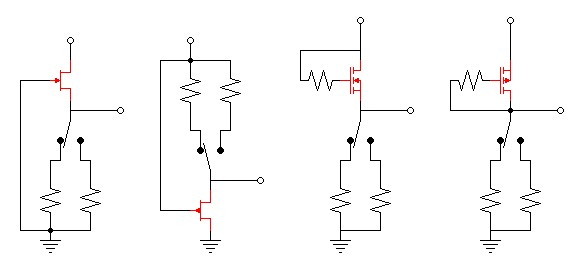

1. Test Circuit Setup

Enhancement MOSFETs tested must be connected so that VBIAS

drops across the selected bias resistor and VGS in

series. JFETs tested must be connected with selected bias

resistor placed between gate and source and sufficient voltage applied

to the drain to ensure device is biased out of its linear range into

saturation. Depletion MOSFETs can be tested the same as

JFETs. If depletion MOSFETs are tested with enhancement bias,

drain voltage cannot be connected with gate voltage as the enhancement

circuit, but sufficient voltage above gate voltage must be applied to

the drain to ensure device is biased out of its linear range into

saturation. Experimentation may be required to determine the best

RBIAS values. At least use values one above and one

below the operating point of your expected circuit.

| Figure

x:

Example

Test

Circuits. Depletion Mode Enhancement Mode NJFET PJFET NMOSFET PMOSFET |

|

2. Soft ware Operation

- Program centers around text editor which recieves the measurement logs.

- Execute Fit Curve dialog by selecting Actions/Fit Data from menu

or clicking related toolbar function (

).

).

- Count will increment by one for each curve fit. Count can be preset by entering a value into its edit control or reset to one by pressing Reset.

- Select Device Type, Device Polarity, and Fit type.

- Enter VBIAS used. This entry will not affect JFET calculations.

- Enter RBIAS and VGS for each

measurement. Values may be entered with the SI prefixes in the

following chart. Program only uses the absolute values of the

entered VGS, polarities are determined instead by the device

type and polarity. For this reason, depletion mode MOSFETs must

not be tested with bias points that would give both positive and

negative values for VGS.

- When data is entered press Fit

button and calculations will appear in the text editor under the Fit

Curve dialog each appended as a separate line. Numeric entry

boxes detect common typing errors and tag them with ? after the error dialog is

dismissed. Improperly formed

data can produce an error result, in which case you should examine the

consistency of your test circuit and measurements.

- After measurements are complete press Exit to leave dialog. The data then may be commented as you desire before saving to a file.

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||

SPICE verification

Program is now SPICE verified. SPICE verification was held up

by confusion of transconductance factor kn with SPICE

tranconductance bulk factor KP.

| (18) |

kn = |

KP

2 |

× |

W

Leff |

Previously, SPICE verification did not seem necessary because of

mathematical correctness to textbook MOSFET equation.

SPICE model for

JFET test set.

SPICE model for

enhancement MOSFET test set.

Software Input Limitations

Because I did not want to accidentally restrict the usefulness of

the program, I have not placed any range limits on the inputs to the

program. At some later time I may place thoughtful and modest

input limitations. Until then, the user is responsible to input

well-formed input data. Therefore, there are a few pitfalls to

beware:

- Choice of two bias resistors should be different. If not, the resulting linear equations will be identical and therefore unsolvable. Even, if the bias resistors are different but close, accuracy of results could suffer.

- Identical VGS values are implausible and result in infinite kn.

- The MOSFET equation defines a entire symmetrical parabola but

only uses a half on one side of VT. If the data is

misformed to place a solution in the undefined region of the parabola,

the results will be invalid. This would occur as a result of

accidentally swapping VGS1 and VGS2. or

calculating MOSFET data as if JFETs or the reverse. As of version

1.1.0, the program now tags the calculated results with the error

message !!alias error!! if

this error is detected.

- Do not choose a zero bias resistor for one bias point of a JFET

thinking to represent a data point at IDSS, as a non-zero

voltage across the resistor is needed for the calculations.

Can it run on Windows 95?

Windows 95 may not have the shared Visual C++ 6.0 dlls needed to run this program. If you have any problem that implicates a missing file, mfc42.dll or msvcrt.dll, download here, and copy into the directory with the program or into the windows system directory (c:\windows\system\ or c:\windows\system32\ whichever contains system dlls).

|

|

1Specifically, Wine

version 1.2.2 under Kubuntu 10.10 Maverick Meerkat. You

will

have

to

copy

mfc42.dll

and/or

mfc42u.dll

to

~/.wine/drive_c/windows/system32 directory for proper operation.

Document History

June 26, 2011 Created.

June 26, 2011 Added section on software input limitations

specifying some data pitfalls, made minor improvements, and clarified a

wordy sentence.

May 31, 2012 Added SPICE verification. Updated program to

version 1.1.0 to flag alias error and to show kn for

transconductance factor to avoid confusion with SPICE parameter KP.

June 2, 2012 Updated program to version 1.2.0 adding input

checking for numeric entries. Immediatedly released version 1.2.1

to allow negative number entry.